Intel 10nm工艺揭秘:晶体管密度比肩台积电/三星7nm

Intel 14nm工艺已经连续用了三代,还要再用一次,10nm则因为良品率始终无法达到满意程度而一再推迟,现在跳票到了2019年,而且上半年还是下半年Intel自己都不确定。

相比之下,台积电、三星已经开始量产7nm,GlobalFoundries 7nm也不远了。

Intel的技术真的不行了?显然不是。虽然都叫xxnm,但是对比之下,Intel无疑是最为严谨的,一直在追求最高的技术指标,也正因为如此再加上半导体工艺难度急剧增加,Intel 10nm才一直难产。

目前,Intel 10nm处理器已经小批量出货,已知产品只有一款低压低功耗的Core i3-8121U,由联想IdeaPad 330笔记本首发。

TechInsight分析了这颗处理器,获得了一些惊人的发现,直接证实了Intel新工艺的先进性。

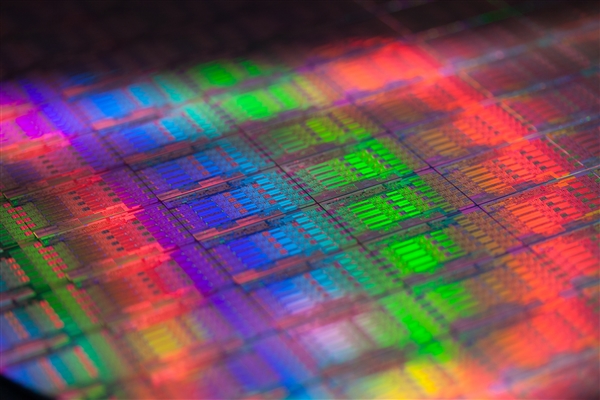

i3-8121U内核局部显微照片

分析发现,Intel 10nm工艺使用了第三代FinFET立体晶体管技术,晶体管密度达到了每平方毫米1.008亿个(符合官方宣称),是目前14nm的足足2.7倍!

作为对比,三星10nm工艺晶体管密度不过每平方毫米5510万个,仅相当于Intel的一半多点,7nm则是每平方毫米1.0123亿个,勉强高过Intel 10nm。

至于台积电、GF两家的7nm,晶体管密度比三星还要低一些。

换言之,仅就晶体管集成度而言,Intel 10nm的确和对手的7nm站在同一档次上,甚至还要更好!

另外,Intel 10nm的最小栅极间距(Gate Pitch)从70nm缩小到54nm,最小金属间距(Metal Pitch)从52nm缩小到36nm,同样远胜对手。

事实上与现有其他10nm以及未来的7nm相比,Intel 10nm拥有最好的间距缩小指标。

Intel 10nm的其他亮点还有:

- BEOL后端工艺中首次使用了金属铜、钌(Ru),后者是一种贵金属

- BEOL后端和接触位上首次使用自对齐曝光方案(self-aligned patterning scheme)

- 6.2-Track高密度库实现超级缩放(Hyperscaling)

- Cell级别的COAG(Contact on active gate)技术

当然了,技术指标再先进,最终也要转换成有竞争力的产品,才算数。

- 全部评论(0)

15015654286 评论 科大讯飞星火认知大:大家好 期待

18458407950 评论 科大讯飞星火认知大:期待期待

17872407701 评论 科大讯飞星火认知大:好期待呀!

13869842415 评论 实践:更改“地区”:不同地区可用信道不同,澳大利亚属于可用信道很多的地区,所

13869842415 评论 实践:更改“地区”:abc就打不动我i大

15015654286 评论 火山引擎增长课堂 新:期待 期待

18139341200 评论 火山引擎增长课堂 新:多多的了解

- 酷冷至尊推出G GOLD V2金牌电源:支持ATX 3.1

- 选主板必须要懂芯片组:一文详解芯片组

- Intel Lunar Lake失去超线程!但多核性能飙升1.5倍

- 微软神秘SSD Z1000揭开面纱:主控厂商曾打败华为!

- 6.2GHz i9-14900KS发布定档3月14日:409W功耗能接受吗

- 6.2GHz i9-14900KS出厂即灰烬!电压高得不可思议

- AMD Zen6架构继续飞跃!核显跨越下下代RDNA5

- 这功耗飞起!RTX 50细节曝光

- Intel Lunar Lake超低功耗处理器首曝:24年的超线程没了!

- Intel 酷睿i9-14900KS下月推出:6.2GHz主频 功耗创纪录

酷冷至尊推出G GOLD V2金牌电源:支持

酷冷至尊推出G GOLD V2金牌电源:支持 选主板必须要懂芯片组:一文详解芯片

选主板必须要懂芯片组:一文详解芯片 Intel Lunar Lake失去超线程!但多核性能

Intel Lunar Lake失去超线程!但多核性能 微软神秘SSD Z1000揭开面纱:主控厂商曾

微软神秘SSD Z1000揭开面纱:主控厂商曾 6.2GHz i9-14900KS发布定档3月14日:409W功耗

6.2GHz i9-14900KS发布定档3月14日:409W功耗 6.2GHz i9-14900KS出厂即灰烬!电压高得不

6.2GHz i9-14900KS出厂即灰烬!电压高得不