AMD Zen5锐龙9000内核布局解密:512位浮点单元大变

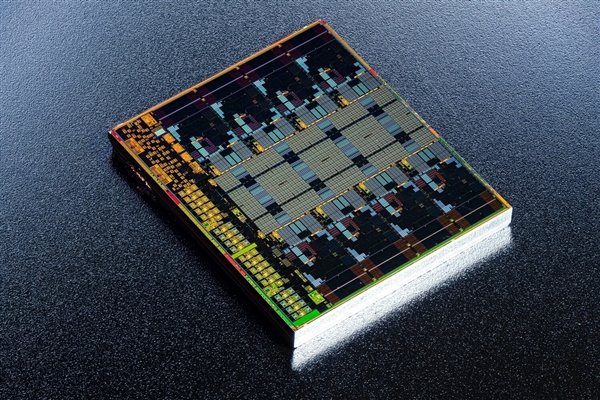

Nemez、Fitzchens Fitz、HighYieldYT等多位大神共同完成了Zen5架构锐龙9000系列的内核解密,包括高清照片、模块分布图。

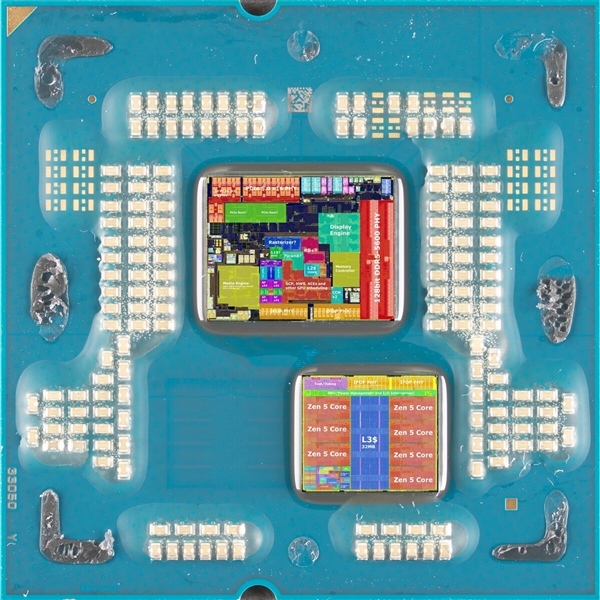

锐龙9000系列延续了chiplet布局,包括一颗或两颗CCD、一颗IOD。

其中,CCD升级架构的同时,制造工艺也从N5 5nm升级为N4P 4nm,IOD则和锐龙7000系列上的完全一样,工艺也还是N6 6nm。

CCD整体布局如上,包括左右两排一共八个Zen5 CPU核心,夹在中间的所有核心共享的32MB三级缓存。

注意看,三级缓存的两排粉色长条区域,和以往一样,是为3D缓存预留的TSV硅通孔,锐龙9000X3D系列上会用到它。

下方是系统管理单元(SMU)、电源管理单元(PMU)、I/O互联模块,以及两个Infinity Fabric高速互连通道模块(IFoP),EPYC上它们的作用更大。

左下角紫色的区域,被标注为测试/调试之用。

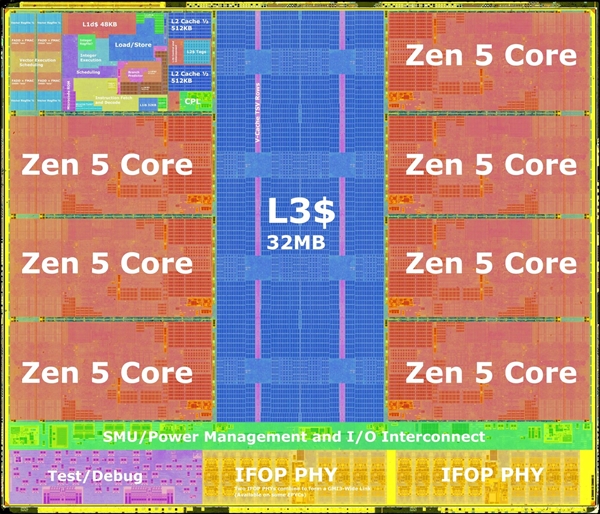

细看每个核心,左侧大片区域是矢量执行单元,主要用作浮点操作,完整支持512位浮点路径,可用于AVX-512指令,所以面积相当大,而且位于核心以及整个CCD的边缘,因为浮点运算发热量大,这样方便散热。

右侧是二级缓存,与之相连的就是三级缓存。

中间部分可以看到指令预取与解码、分支预测、微操缓存、调度器等组成的最重要的前端模块,以及32KB一级指令缓存、48KB一级数据缓存、整数执行单元、载入/存储单元。

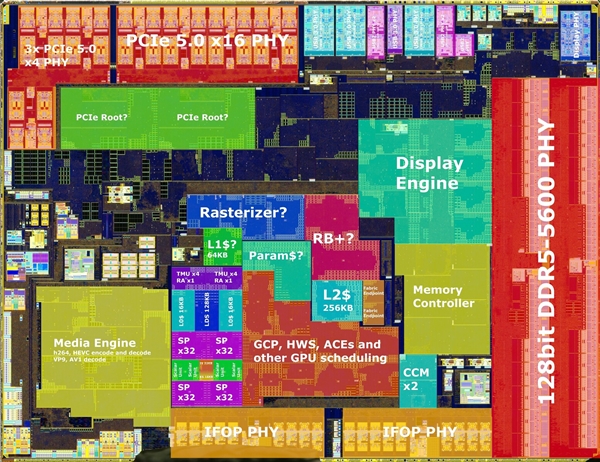

IOD部分没啥新鲜的,128个流处理器的GPU核心、显示引擎、多媒体引擎、128-bit DDR5-5600内存控制器、28条PCIe 5.0控制器、USB 3.x/2.0控制器、两个IFoP端口。

是的,没有原生USB4,X870E/X870上的接口都来自板载第三方主控。

- 全部评论(0)

15015654286 评论 科大讯飞星火认知大:大家好 期待

18458407950 评论 科大讯飞星火认知大:期待期待

17872407701 评论 科大讯飞星火认知大:好期待呀!

13869842415 评论 实践:更改“地区”:不同地区可用信道不同,澳大利亚属于可用信道很多的地区,所

13869842415 评论 实践:更改“地区”:abc就打不动我i大

15015654286 评论 火山引擎增长课堂 新:期待 期待

18139341200 评论 火山引擎增长课堂 新:多多的了解

- AMD Zen5锐龙9000内核布局解密:512位浮点单元大变

- 最高32GB显存!RTX 50系爆料信息汇总

- 联力推出鬼斧Lancool 207中塔机箱:电源前置90度设计

- FAT32支持到2TB了 但exFAT格式才是你的首选

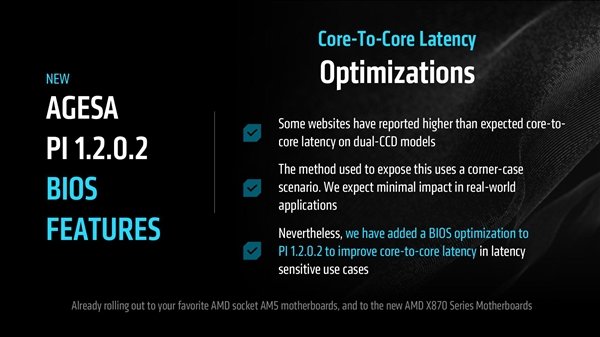

- AMD锐龙9000两大补丁正式发布!延迟大降58%、性能提升35%

- 芝奇发布DDR5-9000 48GB内存:AMD专用!但不适合锐龙9000

- CUDIMM DDR5内存突然爆火!七彩虹上来就是9600MHz

- 128核心500W功耗!AMD Zen5 EPYC提前走光

- AMD锐龙也支持CUDIMM DDR5内存:频率远不如Intel

- 锐龙9000X3D越来越近!锐龙7 9800X3D首发

AMD Zen5锐龙9000内核布局解密:512位浮点

AMD Zen5锐龙9000内核布局解密:512位浮点 最高32GB显存!RTX 50系爆料信息汇总

最高32GB显存!RTX 50系爆料信息汇总 联力推出鬼斧Lancool 207中塔机箱:电源

联力推出鬼斧Lancool 207中塔机箱:电源 FAT32支持到2TB了 但exFAT格式才是你的首

FAT32支持到2TB了 但exFAT格式才是你的首 AMD锐龙9000两大补丁正式发布!延迟大

AMD锐龙9000两大补丁正式发布!延迟大 芝奇发布DDR5-9000 48GB内存:AMD专用!但

芝奇发布DDR5-9000 48GB内存:AMD专用!但